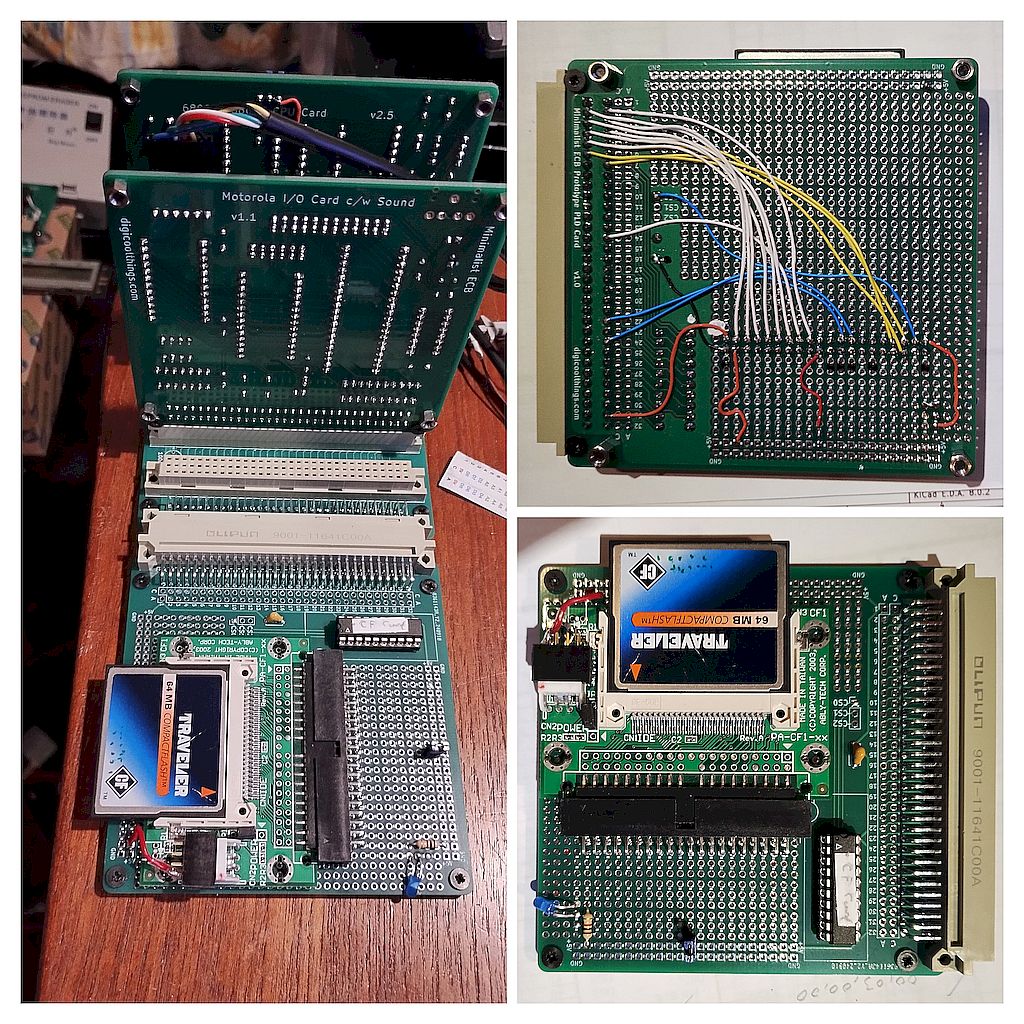

First off I ordered a set of boards and some custom components. I have been collecting various parts for this for some time, but still needed a few more bits and pieces too, clock generators and crystals were last to arrive here. The boards took just under one week from deciding to place an order to having them delivered from JLCPCB.

I started with the 6809 CPU and Motorola I/O cards and when these started to work I built a TMS9918 and the TLS SYS I/O board. I was very happy when I ran the Christmas video and sound demo. I have the 6522 working too. I have no software to try the SCC2691 yet so this bit will have to wait.

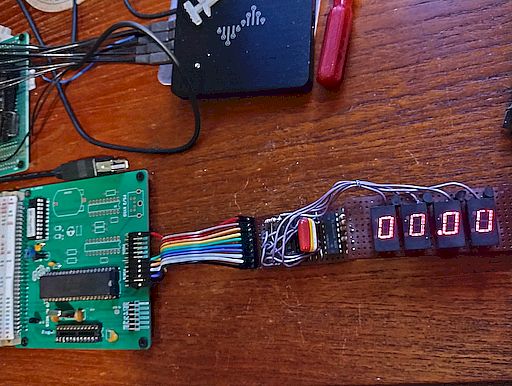

For testing the Angel components I have built a prototype card to interface an HD44780 LCD display and 6551 UART. debugging this card took a day, a couple of faults were fixed. firstly I had to include the 'E' clock into the address decode for the display, and secondly I has the 'A0' and 'A1' address bus signals swapped. The LCD is showing the sign-on message from my old monitor initialisation code.

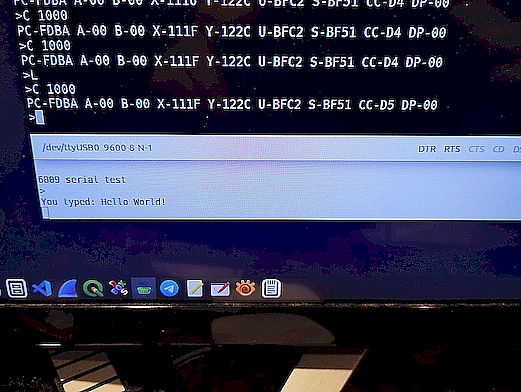

What I have found out is that the original UART, a 6551 is broken. The replacements are working 65C51 (but with txd bugs). I have test software running with both and some old 6551 on order. Here showing what I typed on a seperate serial port when the test program was run.

Before the system was built I patched Greg's ASSIST09 monitor with the Disassembler to use the 6840 single step feature. I added a feature to show the next instruction during tracing, a bit handy when following listings etc.

Code: Select all

>R

PC-F842 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF51 CC-D4 DP-00

PC-1000

>.OP-34 16 PSHS X,B,A

PC-1061 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF4F CC-D4 DP-00

>.OP-30 8C AD LEAX $AD ,PCR

PC-1063 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF4B CC-D4 DP-00

>.OP-BF 10 15 STX $1015

PC-1066 A-00 B-00 X-1013 Y-E002 U-BFC2 S-BF4B CC-D0 DP-00

>.OP-35 96 PULS PC,X,B,A

PC-1069 A-00 B-00 X-1013 Y-E002 U-BFC2 S-BF4B CC-D0 DP-00

>.OP-20 43 BRA $1047

PC-1002 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF51 CC-D0 DP-00

>.OP-34 16 PSHS X,B,A

PC-1047 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF51 CC-D0 DP-00

>.OP-30 8D 00 B4 LEAX $00B4 ,PCR

PC-1049 A-00 B-00 X-20FE Y-E002 U-BFC2 S-BF4D CC-D0 DP-00

>.OP-A6 80 LDA ,X+

PC-104D A-00 B-00 X-1101 Y-E002 U-BFC2 S-BF4D CC-D0 DP-00

>.OP-E6 80 LDB ,X+

PC-104F A-06 B-00 X-1102 Y-E002 U-BFC2 S-BF4D CC-D0 DP-00

>.OP-8D 74 BSR $10C7

PC-1051 A-06 B-30 X-1103 Y-E002 U-BFC2 S-BF4D CC-D0 DP-00

>.OP-7D C8 E0 TST $C8E0

PC-10C7 A-06 B-30 X-1103 Y-E002 U-BFC2 S-BF4B CC-D0 DP-00

>.OP-2B FB BMI $10C7

PC-10CA A-06 B-30 X-1103 Y-E002 U-BFC2 S-BF4B CC-D8 DP-00

>.��

In the screen capture above you can see the debug crash and some garbage appear on the screen, this was happening with the original 2k Assit09 version too, something to investigate. An enhancement I'm thinking of adding is Assis09 trap decoding to help disassembly through system SWI calls. The problem seems to be related to tracing through I/O access instructions maybe some unexpected interaction happening here.

Next I'll maybe try and get my old keyboard working, it depends on having a 6522 available. When some more glue chips arrive I can try the 6502 board and test the SCC2691.

nb, I used some alternative components from stock for the CPU board. The RAM is is a 61c1024-15, for this I needed to tie pin 31 to Vcc to use the top half of its address space. The system rom is a flash part W27C512 set to RO with the jumper, again to use just the top half of address space. I found some old 6809s on ebay this week which I bought, one is a 'C' part som some speed test are in order...

Best regards, David.