Re: Struggling with EEPROM addressing ...

Posted: Fri Jul 12, 2024 11:22 am

Progress: address LEDs look good for function call now (so EEPROM and SRAM working). Not reliable in terms of startups (probably the test rig).

The only thing I did was properly clean the solder side of the board. Also, too many LEDs directly on the 6502 on the address bus seemed less reliable.

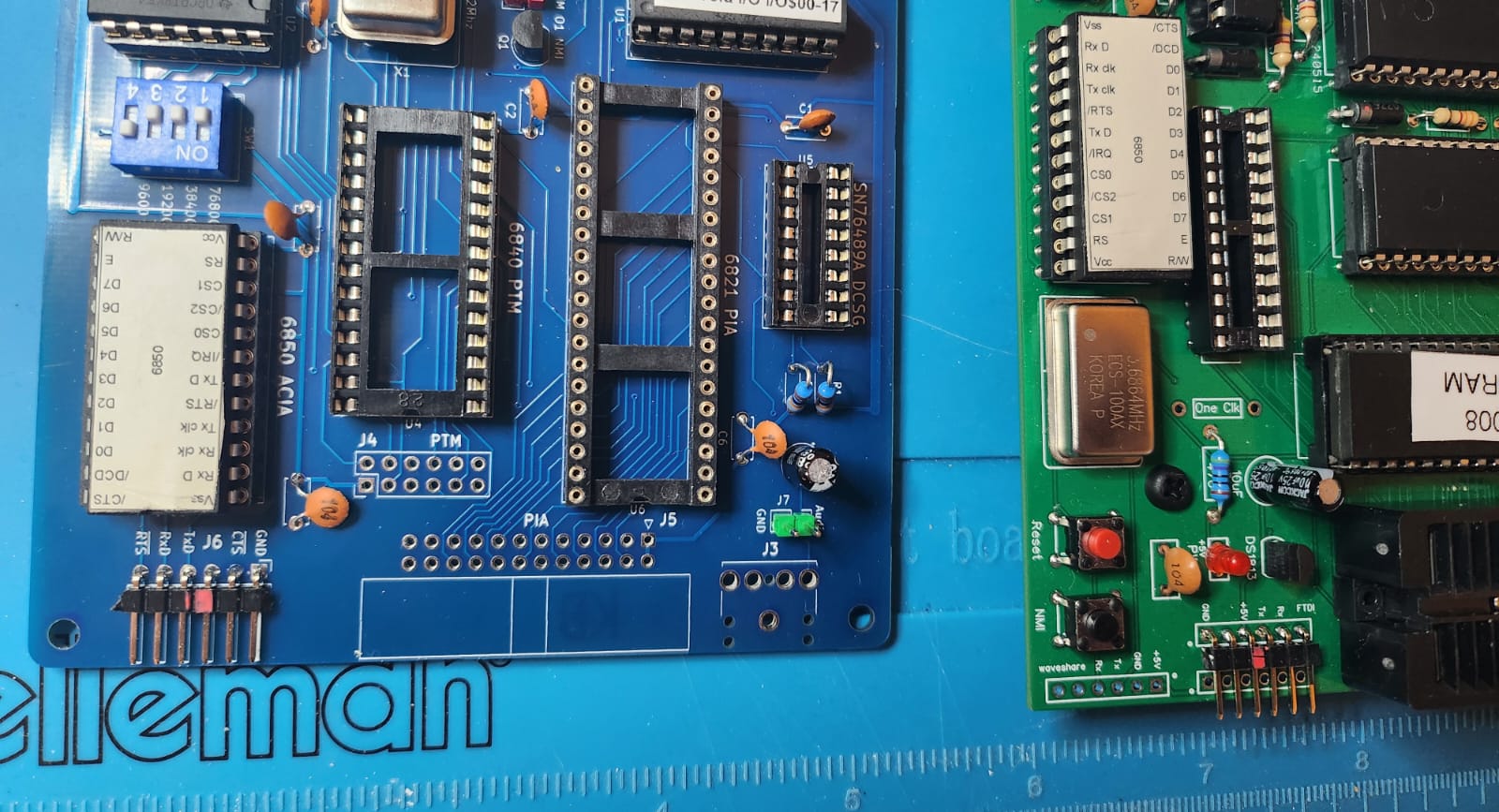

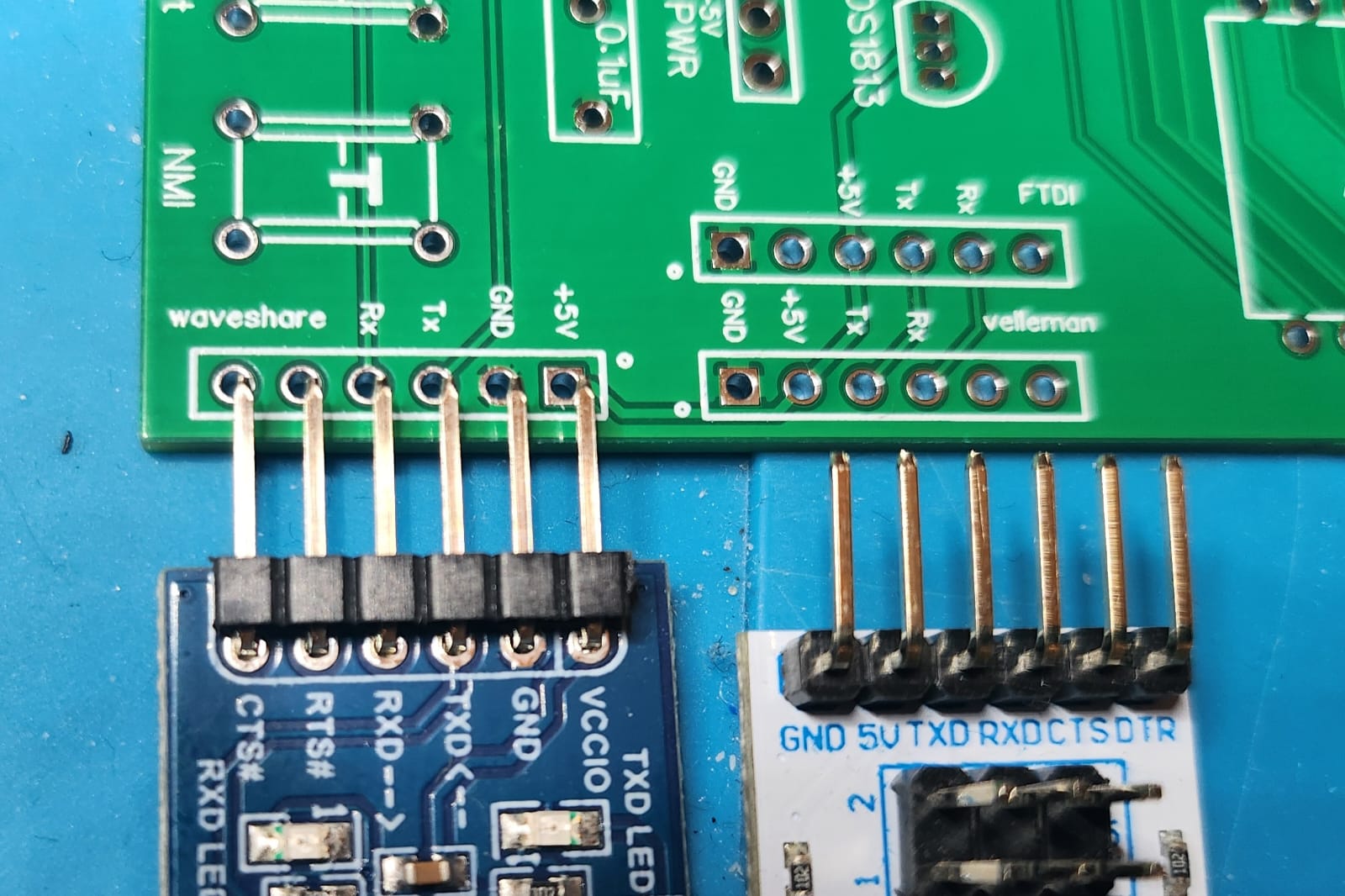

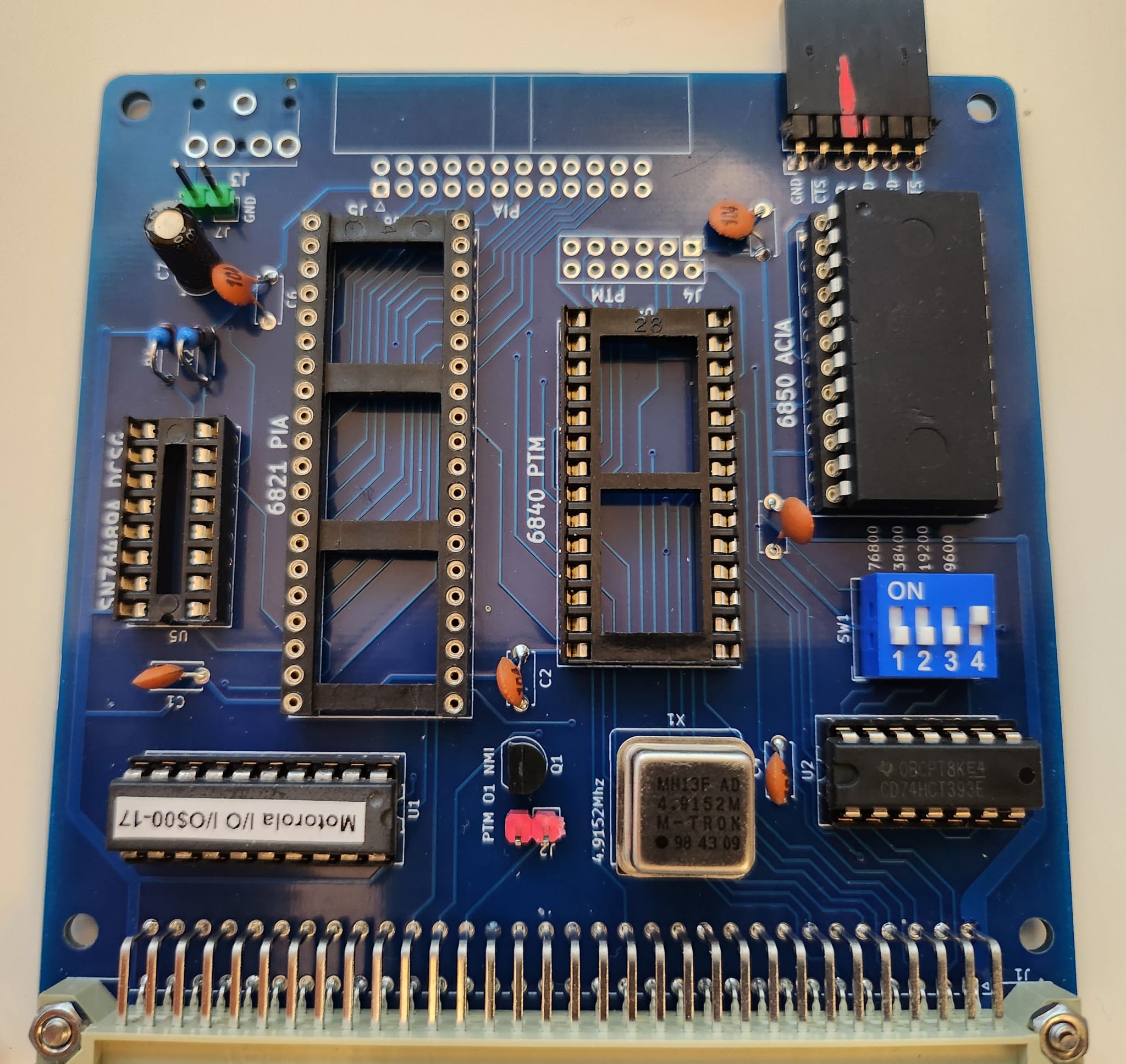

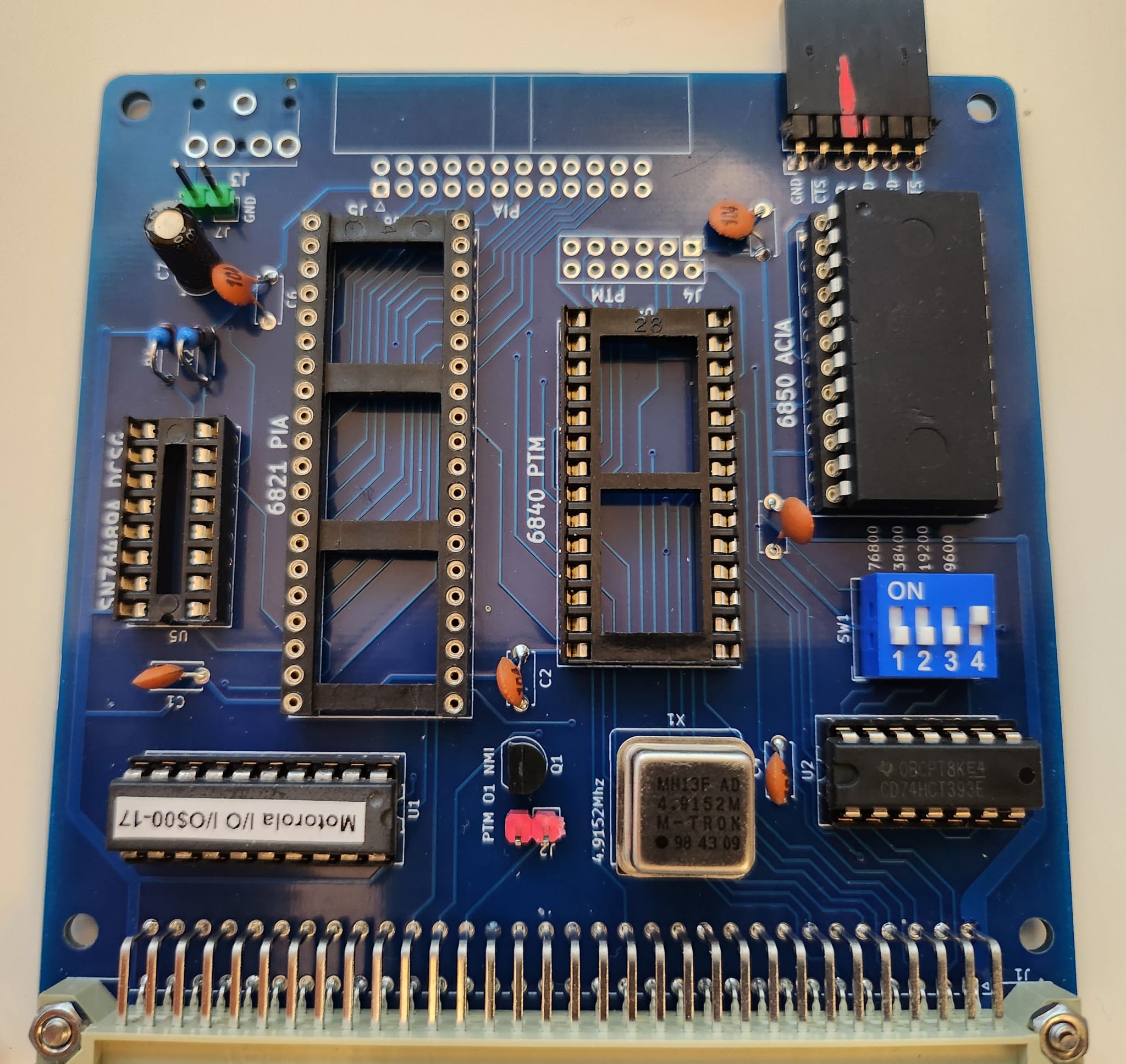

Next: tried to get the ACIA "hello world" working. Depopulated the I/O card to what I assume is the minimum for just using the ACIA.

Spot anything obvious? Running at 9600 for now.

My version of hello world:

The only thing I did was properly clean the solder side of the board. Also, too many LEDs directly on the 6502 on the address bus seemed less reliable.

Next: tried to get the ACIA "hello world" working. Depopulated the I/O card to what I assume is the minimum for just using the ACIA.

Spot anything obvious? Running at 9600 for now.

My version of hello world:

Code: Select all

// constant data

0xF000 0x5C 0x72 0x5C 0x6E 0x48 0x65 0x6C 0x6C 0x6F 0x20 0x36 0x35 0x30 0x32 0x20 0x57 // \r\nHello.6502.W

0xF010 0x6F 0x72 0x6C 0x64 0x21 0x5C 0x72 0x5C 0x6E 0x00 // orld!\r\n.

// /Source/Testing/Minimal/hello.asm:33

// #### HelloMECB.Hopper() #### 0x0000

0xF01A 0xD8 CLD

0xF01B 0xA2 0xFF LDX # 0xFF

0xF01D 0x9A TXS

0xF01E 0x78 SEI // SEI Disable Interrupts hello.asm:35

0xF01F 0xD8 CLD // CLD Clear Decimal flag (Binary mode)

0xF020 0xA2 0xFF LDX # 0xFF // LDX # 0xFF Initialise Stack pointer ($01FF)

0xF022 0x9A TXS // TXS hello.asm:38

0xF023 0xA9 0x03 LDA # 0x03 // LDA # 0x03 hello.asm:41

0xF025 0x8D 0x08 0xE0 STA 0xE008 // STA ACIA Reset ACIA hello.asm:42

0xF028 0xA9 0x51 LDA # 0x51 // LDA # 0b01010001 Receive interrupt disabled, Transmit interrupt disabled, 8 bits, 2 stop bits, no parity, /16 clock,

0xF02A 0x8D 0x08 0xE0 STA 0xE008 // STA ACIA hello.asm:46

0xF02D 0xA2 0x00 LDX # 0 // LDX # 0x00 Initialise character offset pointer

0xF02F 0xA9 0x02 LDA # 0x02 // LDA #0x02 Transmit Data Register Empty flag mask

0xF031 0x2C 0x08 0xE0 BIT 0xE008 // BIT ACIA Is Transmit Data Register Empty?

0xF034 0xF0 0x03 BEQ 0xF039 (+3) // if (Z) { continue; } Loop if not empty

0xF036 0x80 0x04 BRA 0xF03C (+4)

0xF038 0xEA NOP

0xF039 0x80 0xF4 BRA 0xF02F (-12)

0xF03B 0xEA NOP

0xF03C 0xBD 0x00 0xF0 LDA 0xF000,X // LDA Hello, X Get next character to send

0xF03F 0xF0 0x03 BEQ 0xF044 (+3) // if (Z) { break; } If it's the zero string terminator, we're done!

0xF041 0x80 0x04 BRA 0xF047 (+4)

0xF043 0xEA NOP

0xF044 0x80 0x08 BRA 0xF04E (+8)

0xF046 0xEA NOP

0xF047 0x8D 0x09 0xE0 STA 0xE009 // STA ACIAtr Send the character

0xF04A 0xE8 INX // INX Increment character offset pointer

0xF04B 0x80 0xE2 BRA 0xF02F (-30) // } hello.asm:61

0xF04D 0xEA NOP

0xF04E 0x80 0xFE BRA 0xF04E (-2) // loop {} Done, so just Loop Forever!

0xF050 0xEA NOP

0xF051 0xDB STP // } hello.asm:63

// /Source/Testing/Minimal/hello.asm:27

// #### HelloMECB.IRQ() #### 0x0001

0xF052 0x40 RTI // } hello.asm:28

// /Source/Testing/Minimal/hello.asm:30

// #### HelloMECB.NMI() #### 0x0002

0xF053 0x40 RTI // } hello.asm:31

0xFFFA 0xF053 // NMI vector

0xFFFC 0xF01A // Reset vector

0xFFFE 0xF052 // IRQ vector